Imperial College London Department of Electrical and Electronic Engineering

## Equality Saturation for Circuit Synthesis and Verification

Samuel Coward

Supervised by George Constantinides and Theo Drane

Submitted in part fulfilment of the requirements for the degree of Doctor of Philosophy in Electrical and Electronic Engineering of Imperial College London and the Diploma of Imperial College, February 2025

Copyright © 2024 Samuel Coward.

The copyright of this thesis rests with the author. Unless otherwise indicated, its contents are licensed under a Creative Commons Attribution-Non Commercial 4.0 International Licence (CC BY-NC). Under this licence, you may copy and redistribute the material in any medium or format. You may also create and distribute modified versions of the work. This is on the condition that: you credit the author and do not use it, or any derivative works, for a commercial purpose. When reusing or sharing this work, ensure you make the licence terms clear to others by naming the licence and linking to the licence text. Where a work has been adapted, you should indicate that the work has been changed and describe those changes. Please seek permission from the copyright holder for uses of this work that are not included in this licence or permitted under UK Copyright Law.

## Statement of Originality

I, Samuel Coward, declare that the work presented in this thesis is my own, and that any other work has been appropriately referenced.

#### Abstract

The core computational components of a modern Application Specific Integrated Circuit (ASIC) are implemented as datapath circuits, typically specified at the Register Transfer Level (RTL). In industry, the design, optimization and verification of such circuits is mostly a manual process performed by skilled engineers. This effort is a worthwhile investment since datapath circuits are usually the most timing critical circuits, occupying a significant proportion of the total circuit area. Unfortunately, due to the aggressive optimizations and inherent logical complexity, datapath circuits are associated with an equally complex verification challenge.

This thesis takes steps towards the automation of the optimization and verification of datapath circuits, developing tools capable of matching manual design performed by skilled engineers. A core idea behind the thesis, is to raise automated datapath optimization to the abstraction level typically explored by human engineers. This thesis proposes an approach that leverages a data structure, the e-graph that was originally invented by the formal methods community. Via an approach they call equality saturation, the compiler community have repurposed this data structure for program optimization. Applying equality saturation to datapath circuit optimization yields significant improvements in circuit power, performance and area, whilst also offering a robust verification flow that provides the correctness guarantees required by industrial circuit design.

This thesis describes a number of theoretical enhancements to equality saturation that permit the expression of new classes of optimization that go beyond those implemented by existing technology. The first of these formalizes the connection between equality saturation and program analysis techniques, creating a positive feedback loop that leads to analysis refinement and deeper exploration. The second, describes an approach to encoding context-awareness in equality saturation, capturing optimizations that stem from constraints expressed within a program.

#### Acknowledgements

First and foremost I wish to express my gratitude to Intel Corporation, not only for funding my PhD, but also for their willingness to experiment with a highly integrated PhD model. The access to Intel engineers, designs and resources has ensured the research is highly relevant in an industrial setting, addressing the difficult questions that remain in modern circuit design. This thesis would not exist without the vision and determination of Theo Drane, the consistent support of Altug Koker and those from both Intel and Imperial that brought both parties to an agreement, in particular Susan Capello and Jing Sheng Pang.

Thanks to the sponsored PhD model, I had the privilege of working with two wonderful supervisors. My deepest gratitude goes to both Theo Drane from Intel and George Constantinides from Imperial. It was a paper pointer from George during the early months of my PhD, that introduced me to the programming languages field and influenced so much of my PhD. George's ability to reduce a problem down to a core theoretical question helped guide me through much of the PhD, and allowed me to connect with a broad range of research communities. Meanwhile, Theo's drive and industrial perspective, pushed the research to not only answer difficult questions in circuit design, but to concisely communicate the solutions to countless different audiences. I would also like to thank my examiners Alastair Donaldson and Tom Melham for their challenging questions and valuable suggestions that have helped to shape this final thesis. Perhaps the most important lesson I learnt, is that the times of greatest success are the times at which it is most important to keep one's feet firmly grounded.

Within Intel, I was fortunate to be part of the Intel Numerical and System Level Design Group, which grew to six full-time staff at its peak. My sincere thanks go to Emiliano Morini for teaching me everything I know about verification and for many laughs along the way, to Rafael Barbalho for sharing his expertise in software design and for his drive to see my research deployed as widely as possible, to Bill Zorn for being an authority on all things programming languages, and to Chris Poole for his unbounded enthusiasm for research. Without this team, the scope of my research would be far more limited and the quality of my tools would be less. More broadly, I have worked with many great people across all parts of Intel. I am grateful to each one of them.

Being physically located in the Circuits and Systems Group (CAS) at Imperial has led to

friendships and collaborations that I have no doubt will stand the test of time. To Aditya, Diederick, Alex M, Ben C, Alex D, Ben B and Zhewen my thanks go to making me feel so welcome at the start of my PhD. I would also like to thank Yann and Jianyi for exciting collaborations and for standing alongside me in the pursuit of better tools for hardware designers. To my travel companion extraordinaire, Marta Andronic, thank you for bringing an unrivaled energy to the office and for bringing positive culture change to CAS. A huge thanks must go to Wiesia Hsissen, who keeps the whole CAS group on track and has made my life easier on countless occasions. There are too many friends to highlight individually but my thanks go to Guoxuan, Mingzhu, Toni, Dan, Ebby, Michalis, Quentin, Pedro, Cheng, Violet, Cano, Keran, John, Omar, Sina and Zehui.

Lastly, it remains to thank the friends and family that supported me along the way. To James Van Der Walt, thank you for inviting me into your home on so many occasions and I can only apologize for any chaos connected to my visits, although I do not take sole responsibility. Thank you to my parents, without the hours spent on times tables in the car and your endless support I would not be where I am today. Of course, many thanks go to my partner Karolina, who has helped me to become a more considerate person, as we have navigated a sometimes challenging but mostly fortunate life together.

The chance to simultaneously span academia and industry has provided opportunities that few will have and I hope that I have made the most of them. To anyone who is fortunate enough to be offered such a role, I would highly recommend it.

## Acronyms

| $\mathbf{AI}$ abstract interpretation        |

|----------------------------------------------|

| ASIC Application Specific Integrated Circuit |

| <b>CSA</b> carry-save adder                  |

| <b>CSD</b> Canonical Signed Digit            |

| <b>DPV</b> Datapath Validation               |

| <b>EC</b> equivalence checking               |

| <b>ECO</b> Engineering Change Order          |

| <b>EDA</b> Electronic Design Automation      |

| <b>FIR</b> Finite Impulse Response           |

| <b>FMA</b> Fused Multiply-Add                |

| <b>FPGA</b> Field Programmable Gate Array    |

| $\mathbf{FV}$ Formal Verification            |

| <b>GPU</b> Graphics Processing Unit          |

| HDL hardware description languages           |

| <b>HLS</b> High-Level Synthesis              |

| IA interval arithmetic                       |

| <b>ILP</b> integer linear programming        |

| <b>IP</b> Intellectual Property              |

| <b>LRM</b> language reference manual         |

| LS Logic Synthesis                           |

| $\mathbf{LZC}$ leading-zero count            |

|                                              |

- ${\bf MCM}\,$  Multiple Constant Multiplication

- $\ensuremath{\mathbf{PPA}}$  power, performance and area

- **RL** reinforcement learning

- **RTL** Register Transfer Level

- ${\bf SAT}$  Satisfiability

- ${\bf SMT}$ Satisfiability Modulo Theories

- **STE** Symbolic Trajectory Evaluation

- $\mathbf{TCAD}$  IEEE Transactions on Computer-Aided Design of Integrated Circuits & Systems

# Contents

| St                  | Statement of Originality i |                               |   |  |  |  |

|---------------------|----------------------------|-------------------------------|---|--|--|--|

| Al                  | Abstract                   |                               |   |  |  |  |

| A                   | cknov                      | vledgements                   | 7 |  |  |  |

| A                   | crony                      | ms vi                         | i |  |  |  |

| Li                  | st of                      | Tables xv                     | 7 |  |  |  |

| List of Figures xvi |                            |                               |   |  |  |  |

| 1                   | Intr                       | oduction                      | L |  |  |  |

|                     | 1.1                        | Problem Statements            | 6 |  |  |  |

|                     | 1.2                        | Contributions                 | 7 |  |  |  |

|                     | 1.3                        | Implementation and Evaluation | 9 |  |  |  |

|                     | 1.4                        | Thesis Outline                | ) |  |  |  |

|                     | 1.5                        | Publications                  | ) |  |  |  |

| 2                   | Bac                        | kground 15                    | 3 |  |  |  |

|                     | 2.1                        | Datapath Circuit Design       | 3 |  |  |  |

|   |                                               | 2.1.1                                                                             | RTL Synthesis                                                                                                                                                    | 14                                                                                                                     |

|---|-----------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|   |                                               | 2.1.2                                                                             | Manual Datapath Design                                                                                                                                           | 18                                                                                                                     |

|   |                                               | 2.1.3                                                                             | Low-Power RTL Design                                                                                                                                             | 19                                                                                                                     |

|   |                                               | 2.1.4                                                                             | High-Level Synthesis                                                                                                                                             | 21                                                                                                                     |

|   | 2.2                                           | Datap                                                                             | ath Formal Verification                                                                                                                                          | 22                                                                                                                     |

|   | 2.3                                           | Progra                                                                            | am Analysis                                                                                                                                                      | 25                                                                                                                     |

|   | 2.4                                           | E-Gra                                                                             | phs and Equality Saturation                                                                                                                                      | 27                                                                                                                     |

|   |                                               | 2.4.1                                                                             | Equality Saturation and Rewriting                                                                                                                                | 27                                                                                                                     |

|   |                                               | 2.4.2                                                                             | Egg                                                                                                                                                              | 30                                                                                                                     |

|   |                                               | 2.4.3                                                                             | Applications                                                                                                                                                     | 31                                                                                                                     |

|   |                                               |                                                                                   |                                                                                                                                                                  |                                                                                                                        |

| 3 | Ciro                                          | cuit Ai                                                                           | rea Minimization via Verified E-Graph Rewriting at the RT-Level                                                                                                  | 33                                                                                                                     |

| 3 | <b>Ciro</b><br>3.1                            |                                                                                   | rea Minimization via Verified E-Graph Rewriting at the RT-Level<br>nediate Representation                                                                        |                                                                                                                        |

| 3 |                                               | Intern                                                                            |                                                                                                                                                                  | 35                                                                                                                     |

| 3 | 3.1                                           | Intern                                                                            | nediate Representation                                                                                                                                           | 35<br>39                                                                                                               |

| 3 | 3.1                                           | Intern<br>Rewri                                                                   | ediate Representation                                                                                                                                            | 35<br>39<br>39                                                                                                         |

| 3 | 3.1                                           | Intern<br>Rewri <sup>*</sup><br>3.2.1<br>3.2.2                                    | nediate Representation                                                                                                                                           | 35<br>39<br>39                                                                                                         |

| 3 | 3.1<br>3.2                                    | Intern<br>Rewri <sup>*</sup><br>3.2.1<br>3.2.2                                    | nediate Representation                                                                                                                                           | 35<br>39<br>39<br>44                                                                                                   |

| 3 | 3.1<br>3.2                                    | Intern<br>Rewrit<br>3.2.1<br>3.2.2<br>Extrac                                      | nediate Representation                                                                                                                                           | 35<br>39<br>39<br>44<br>49                                                                                             |

| 3 | 3.1<br>3.2                                    | Intern<br>Rewrit<br>3.2.1<br>3.2.2<br>Extrac<br>3.3.1                             | nediate Representation                                                                                                                                           | <ol> <li>35</li> <li>39</li> <li>39</li> <li>44</li> <li>49</li> <li>49</li> <li>50</li> </ol>                         |

| 3 | 3.1<br>3.2                                    | Intern<br>Rewrit<br>3.2.1<br>3.2.2<br>Extrao<br>3.3.1<br>3.3.2<br>3.3.3           | nediate Representation   tes Specifying Rewrites Synthesizing Rewrite Conditions etion and Back-End Cost Model Cost Model Common Sub-Expression Aware Extraction | <ol> <li>35</li> <li>39</li> <li>39</li> <li>44</li> <li>49</li> <li>49</li> <li>50</li> </ol>                         |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Intern<br>Rewri<br>3.2.1<br>3.2.2<br>Extrac<br>3.3.1<br>3.3.2<br>3.3.3<br>Verific | nediate Representation                                                                                                                                           | <ol> <li>35</li> <li>39</li> <li>39</li> <li>44</li> <li>49</li> <li>49</li> <li>50</li> <li>51</li> <li>52</li> </ol> |

|   |     | 3.5.2 Exploiting Datapath Optimizations                        | 56 |

|---|-----|----------------------------------------------------------------|----|

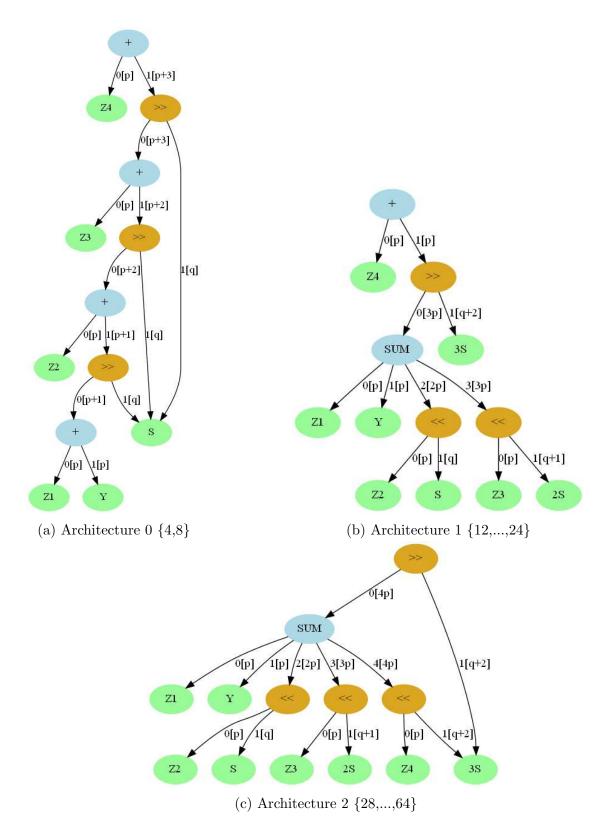

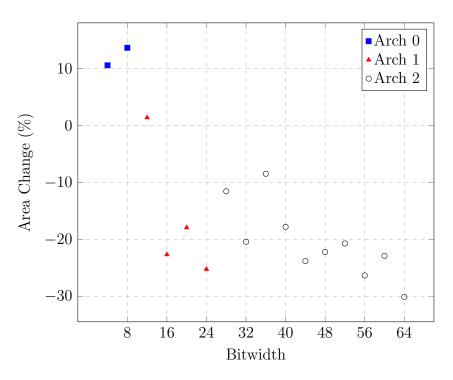

|   |     | 3.5.3 Bitwidth Dependent Architectures                         | 59 |

|   |     | 3.5.4 Performance                                              | 61 |

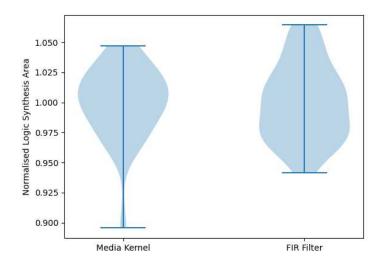

|   | 3.6 | Cost Metric Evaluation                                         | 62 |

|   | 3.7 | Summary                                                        | 65 |

| 4 | Con | nbining Equality Saturation with Abstract Interpretation       | 66 |

|   | 4.1 | Theory                                                         | 70 |

|   |     | 4.1.1 Abstraction                                              | 70 |

|   |     | 4.1.2 Application to E-graphs                                  | 72 |

|   |     | 4.1.3 Cyclic E-graphs and Fixpoints                            | 74 |

|   | 4.2 | Implementation                                                 | 76 |

|   | 4.3 | Results                                                        | 78 |

|   |     | 4.3.1 Benchmark Selection                                      | 80 |

|   |     | 4.3.2 Evaluation                                               | 80 |

|   |     | 4.3.3 Iterative Method Discovery                               | 80 |

|   | 4.4 | Summary                                                        | 82 |

| 5 | Aut | comating Constraint-Aware Datapath Optimization using E-Graphs | 84 |

|   | 5.1 | Localizing Constraint-Aware Optimization                       | 87 |

|   |     | 5.1.1 Sub-Domain Equivalence                                   | 87 |

|   |     | 5.1.2 Sub-Domain Equivalence in an E-Graph                     | 88 |

|   |     | 5.1.3 Program Analysis Refinement                              | 91 |

|   | 5.2 | RTL Performance Optimization                                   | 95 |

|   |     | 5.2.1  | Value Range Analysis                                      | 96  |

|---|-----|--------|-----------------------------------------------------------|-----|

|   |     | 5.2.2  | Constraint and Value Range Aware RTL Rewriting            | 99  |

|   |     | 5.2.3  | Extraction                                                | 102 |

|   | 5.3 | Result | 58                                                        | 104 |

|   |     | 5.3.1  | Case-Study: Floating-Point Subtract                       | 105 |

|   |     | 5.3.2  | Multi-Objective Optimization                              | 109 |

|   |     | 5.3.3  | Benchmark Selection                                       | 112 |

|   |     | 5.3.4  | Delay Optimization Evaluation                             | 114 |

|   | 5.4 | Summ   | ary                                                       | 116 |

| 6 | Cor | nbinin | g Power and Arithmetic Optimization via E-Graph Rewriting | 117 |

|   | 6.1 | Encod  | ling Power Optimizations                                  | 119 |

|   |     | 6.1.1  | Data Gating                                               | 120 |

|   |     | 6.1.2  | Clock Gating                                              | 123 |

|   | 6.2 | Power  | Estimation and Extraction                                 | 125 |

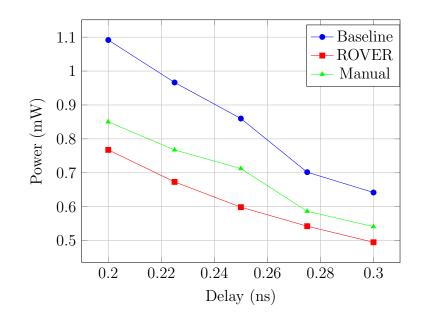

|   |     | 6.2.1  | Simulation                                                | 125 |

|   |     | 6.2.2  | Operator Power Model                                      | 127 |

|   | 6.3 | Result | 5 <b>8</b>                                                | 128 |

|   |     | 6.3.1  | Benchmark Selection                                       | 130 |

|   |     | 6.3.2  | Dynamic Power Reduction                                   | 130 |

|   |     | 6.3.3  | Data Dependent Design                                     | 133 |

|   | 6.4 | Summ   | ary                                                       | 134 |

| 7  | For             | mal Verification and Bug Fixing via E-Graph Rewriting | 135 |

|----|-----------------|-------------------------------------------------------|-----|

|    | 7.1             | ROVERIFY: A Formal Verification Assistant             | 139 |

|    |                 | 7.1.1 E-Graph Initialization                          | 139 |

|    |                 | 7.1.2 Bitwidth Dependent Verification Rewrites        | 140 |

|    |                 | 7.1.3 Maximal Sharing Extraction                      | 142 |

|    | 7.2             | ROVERIFY Case-Study                                   | 145 |

|    | 7.3             | ROVERIFIX: Automatic Bug Fixing                       | 147 |

|    | 7.4             | ROVERIFY Results                                      | 149 |

|    |                 | 7.4.1 Benchmark Selection                             | 150 |

|    | 7.5             | Summary                                               | 153 |

| 8  | Con             | clusion                                               | 155 |

|    | 8.1             | E-Graph and Equality Saturation Outlook               | 156 |

|    | 8.2             | Directions in Digital Circuit Design                  | 158 |

|    |                 | 8.2.1 Pipelining and Retiming                         | 158 |

|    |                 | 8.2.2 Approximate Computing                           | 159 |

|    | 8.3             | Software Roadmap                                      | 159 |

|    | 8.4             | Final Remarks                                         | 160 |

| Re | e <b>fere</b> i | nces                                                  | 162 |

| Al | ppen            | dices                                                 | 181 |

| A  | Ben             | chmarks                                               | 182 |

| в  | Ass             | ociativity of Addition Condition                      | 183 |

## C SMT Encoding of Motivational Example

# List of Tables

| 3.1 | VeriLang operator table                                                   |

|-----|---------------------------------------------------------------------------|

| 3.2 | ROVER datapath rewrites                                                   |

| 3.3 | Evaluation of ROVER optimizations                                         |

| 3.4 | ROVER performance                                                         |

| 4.1 | Interval arithmetic rewrites                                              |

| 5.1 | ASSUME node rewrites                                                      |

| 5.2 | RTL comparator rewrites to aid analysis refinement                        |

| 5.3 | Additional VeriLang operator table                                        |

| 5.4 | Dynamic and conditional rewrites exploiting domain knowledge              |

| 5.5 | Constraint-aware ROVER synthesis results for performance optimization 113 |

| 6.1 | Power optimization rewrites                                               |

| 6.2 | Circuit power optimization synthesis results                              |

| 6.3 | Switching activity configuration comparison table                         |

| 7.1 | Verification rewrite set                                                  |

| 7.2 | Bug Fixing Rewrites                                                       |

| 7.3 | ROVERIFY benchmark results                   | 150 |

|-----|----------------------------------------------|-----|

| 7.4 | ROVERIFY e-graph summary                     | 152 |

| A.1 | Summary of benchmarks used throughout thesis | 182 |

# List of Figures

| 1.1 | Circuit Design Flow Comparison                                | 3  |

|-----|---------------------------------------------------------------|----|

| 1.2 | Synthesis Tool Comparison                                     | 5  |

| 1.3 | Design cost progress during rewriting                         | 5  |

| 1.4 | Tool and library suite                                        | 7  |

| 2.1 | Operand isolation optimization                                | 20 |

| 2.2 | Equivalence checking tool overview                            | 24 |

| 2.3 | Waterfall approach to equivalence checking                    | 25 |

| 2.4 | E-graph rewriting example                                     | 28 |

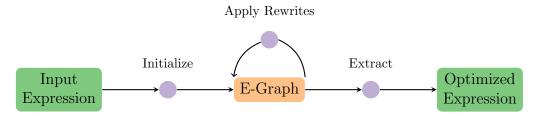

| 2.5 | Equality saturation flow                                      | 29 |

| 3.1 | ROVER flow diagram                                            | 34 |

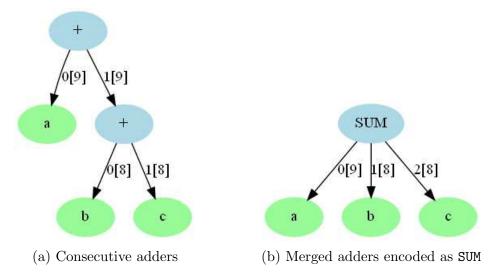

| 3.2 | Merging arithmetic operations using carry-save representation | 38 |

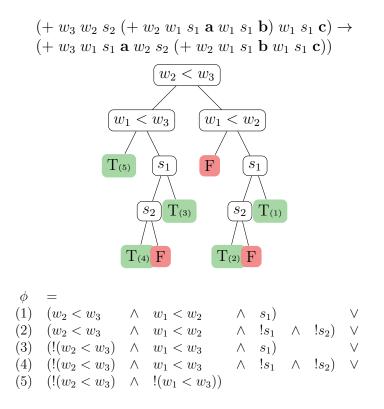

| 3.3 | Associativity of addition rewrite                             | 41 |

| 3.4 | ROVER flow diagram                                            | 45 |

| 3.5 | Decision tree classifier for associativity rewrite            | 46 |

| 3.6 | Area-delay profile for Media Kernel                           | 54 |

| 3.7 | Shift Mult Benchmark                                          | 57 |

| 3.8  | Bitwidth dependent architecture selection                          | 60  |

|------|--------------------------------------------------------------------|-----|

| 3.9  | Synthesis results for bitwidth dependent architecture selection    | 61  |

| 3.10 | Violin plot of synthesis noise                                     | 63  |

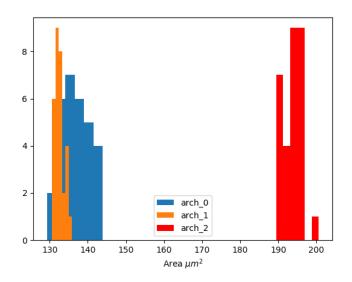

| 3.11 | Histogram plot of synthesis noise                                  | 63  |

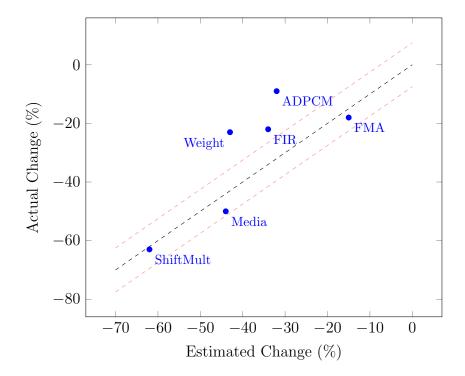

| 3.12 | Correlation between ROVER's cost model and logic synthesis results | 64  |

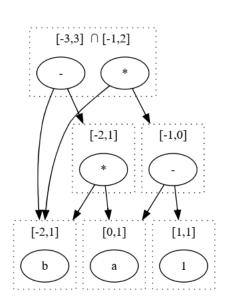

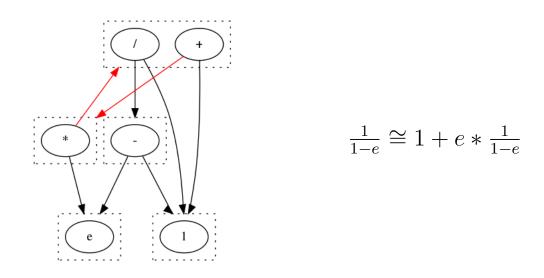

| 4.1  | Interval analysis e-graph example                                  | 68  |

| 4.2  | Positive feedback loop of e-graph rewriting and analysis           | 69  |

| 4.3  | Abstract property propagation algorithm                            | 73  |

| 4.4  | Cyclic e-graph                                                     | 74  |

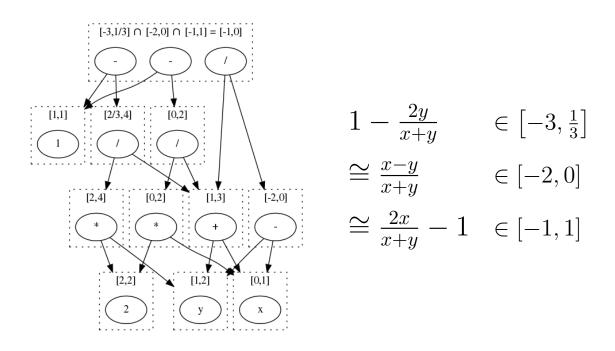

| 4.5  | Three expression interval analysis e-graph                         | 79  |

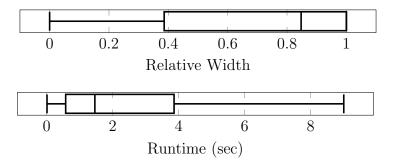

| 4.6  | Relative interval width of e-graph analysis                        | 79  |

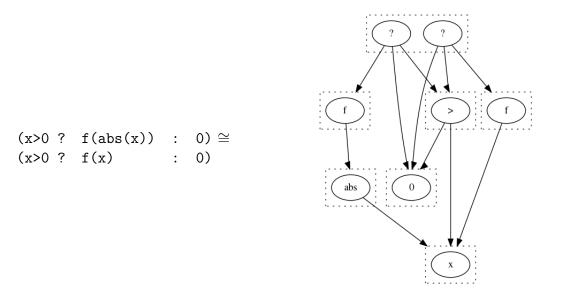

| 5.1  | E-graph representing a constraint-aware optimization               | 85  |

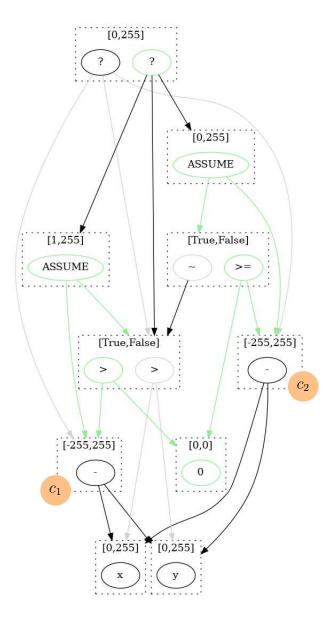

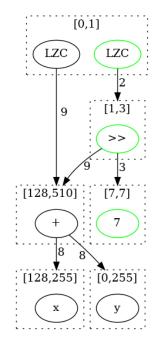

| 5.2  | E-graph abstraction refinement via ASSUME nodes                    | 93  |

| 5.3  | Constraint-aware ROVER flow diagram                                | 96  |

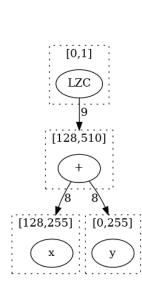

| 5.4  | E-graph rewriting of a leading zero count optimization             | 100 |

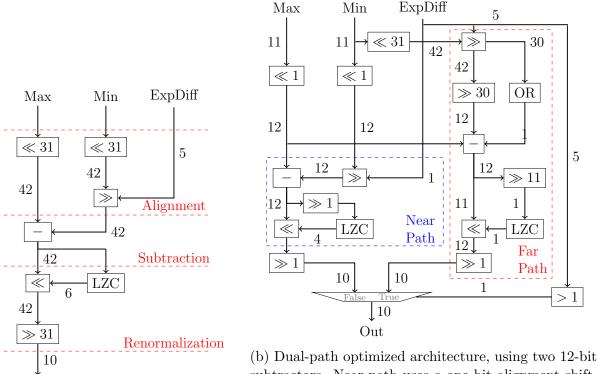

| 5.5  | Half-precision floating-point subtraction case-study               | 108 |

| 5.6  | Alternative case split designs for floating-point subtractor       | 109 |

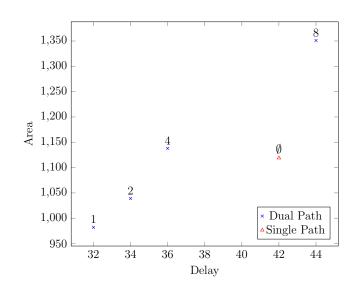

| 5.7  | Area-delay profiles for ROVER optimized floating-point subtractors | 110 |

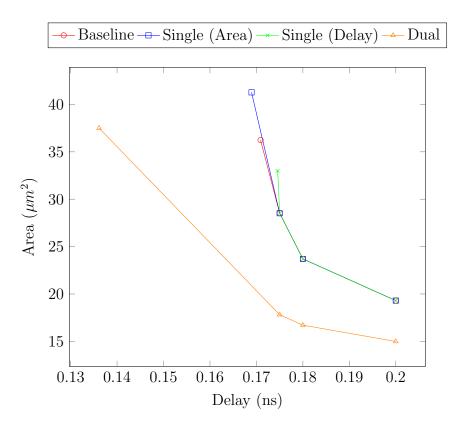

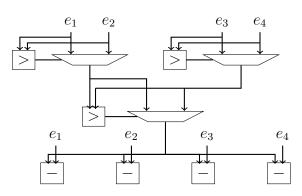

| 5.8  | Exponent max tree case-study                                       | 111 |

| 5.9  | Pareto frontier of ROVER generated max tree implementations        | 111 |

| 6.1  | Operand isolation optimization                                     | 118 |

| 6.2 | ROVER's power optimization tool flow                                         |

|-----|------------------------------------------------------------------------------|

| 6.3 | Transparent and enabled register circuit diagrams                            |

| 6.4 | Stimuli generation algorithm                                                 |

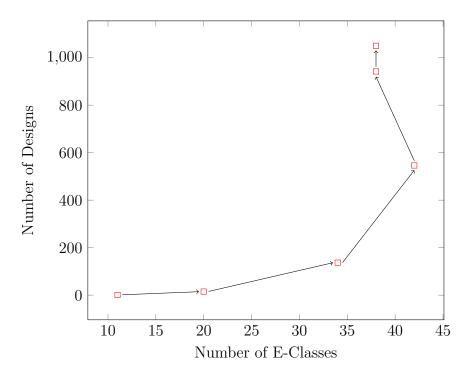

| 6.5 | Number of designs represented by the e-graph vs. the number of e-classes 127 |

| 6.6 | Delay-power profile                                                          |

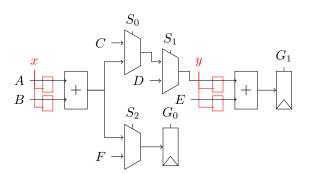

| 6.7 | Pipelined Mux Add Tree benchmark diagram                                     |

| 7.1 | Motivational example breaking existing equivalence checking tools            |

| 7.2 | ROVERIFY flow diagram                                                        |

| 7.3 | E-graph representation of motivational example                               |

| 7.4 | ROVERIFY generated verification waterfall                                    |

| 7.5 | E-graph convergence for motivational example                                 |

| 7.6 | ROVERIFIX flow diagram                                                       |

| 7.7 | ROVERIFIX motivational example                                               |

| 7.8 | Box Filter dataflow graph                                                    |

| 8.1 | Tool and library suite                                                       |

## Chapter 1

## Introduction

In 2020, global microchip manufacturing reached one trillion units, according to a European Union report that also projects semiconductor demand will double between 2022 and 2030 [1]. This means that the need for efficient digital circuit design techniques is greater than ever. All digital circuit design approaches pair a skilled engineer (or team of engineers) with a suite of automatic design and verification tools. Unfortunately, consolidation in the Electronic Design Automation (EDA) industry has left engineers with few core design tools to choose from.

In 2024 there are broadly two classes of approach to digital circuit design. The first, more mature method, defines a digital circuit and its timing behavior at the RT-level, using an entrenched hardware description languages (HDL) such as Verilog [2] or VHDL [3]. The second, more recently developed approach, High-Level Synthesis (HLS) [4, 5, 6, 7], allows engineers to write their digital circuit designs at a higher level of abstraction, using extensions of software languages like C++. HLS tools consume these high-level circuit designs that do not specify the circuit's timing behavior. The HLS tool performs the complex steps to generate a functionally equivalent RTL design with the appropriate timing behavior. In both cases, the RTL generated is passed onto a Logic Synthesis (LS) tool [8, 9], the next step in the digital circuit design tool flow. Both design flows rely on graph representations of digital circuits, a dataflow graph for encoding data dependencies and a control flow graph for encoding possible execution paths. Accompanying the circuit design process is an architect, who also takes the natural language

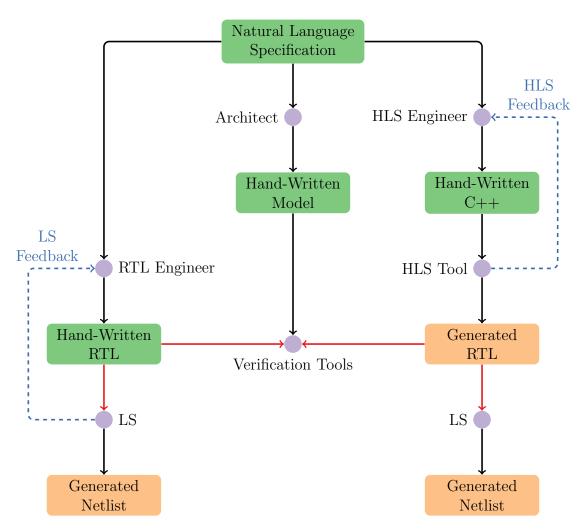

specification and produces a model, usually in a language like C++. Using a suite of verification tools the RTL implementations are verified against this model by a verification engineer, feeding any bugs back to the design engineers. Figure 1.1 illustrates the alternative methodologies and the respective tool feedback loops. In their current form, neither approach allows engineers to efficiently deliver high-performance and provably correct digital circuit designs, particularly for datapath circuits.

A challenge in the low-level design approach is that in addition to specifying the circuit's functional and timing behavior, the RTL engineer must also consider their power, performance and area (PPA) targets. Whilst LS performs many complex optimizations, it operates on a mostly fixed dataflow graph. For RTL written at a word-level of abstraction, LS will not reorder operations or apply many higher-level transformations, such as local resource sharing. This thesis will demonstrate that such techniques offer significant PPA improvements. My experience in Intel has shown how expert RTL engineers manually optimize their HDL code to realize these PPA gains. Often this involves iteratively running LS to evaluate the impact of the most recent changes, further refining the design based on reports generated by LS. Unfortunately, this is both bug prone and time consuming due to the long LS compile times, reducing the productivity of the design flow.

In the high-level design flow, the engineer no longer needs to specify the timing behavior but currently, nothing in the design flow performs the PPA optimizations implemented by the experienced RTL engineer. The HLS engineer is not expected to understand low-level digital circuit design principles, nor do the input languages allow them to succinctly express the same optimizations. Meanwhile, whilst HLS tools have matured significantly, they currently defer datapath optimizations to LS which, as already discussed, lacks the capabilities of expert engineers. For custom datapath designs, my experience and the continuing prevalence of RTL suggests that circuits designed using these high-level techniques are unable to match the PPA of those produced using the low-level approach, limiting industrial application to prototyping exercises. The introduction of a tool-chain, where LS consumes the output of HLS, introduces a potential correlation problem, where the circuit quality predicted by HLS may not match that produced by LS. Such mismatches can be frustrating, if not impossible, to resolve and

Figure 1.1: A comparison of digital circuit design flow methodologies. Red arrows denote where the design techniques described in this thesis are applied.

more importantly they could drive the HLS tool to make poor design decisions. Compounding the problem, many HLS tools lack an associated formal verification flow that can prove the correctness of the generated RTL, although Cadence's Stratus [6] is now more tightly integrated with the Jasper verification platform [10].

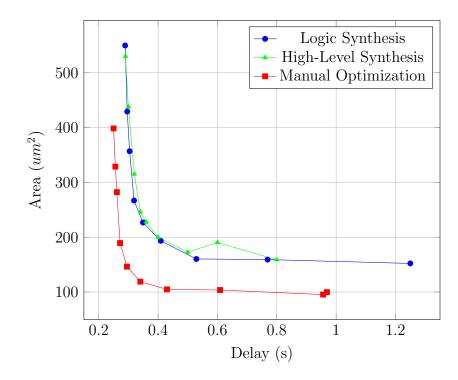

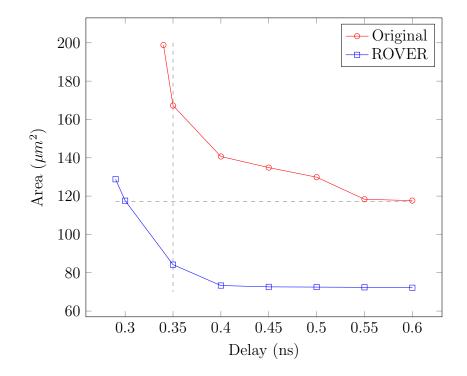

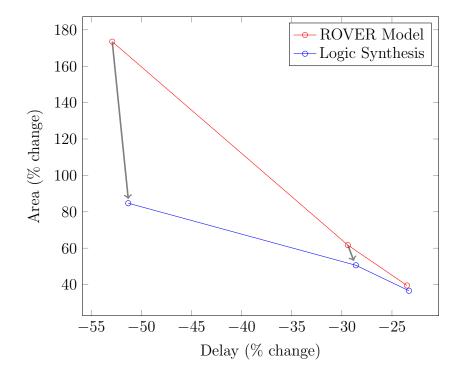

The above discussion highlights a gap between the high-level software optimizations performed by HLS and the low-level optimizations performed by tools like LS. Crucially this underexplored gap holds the potential for substantial gains in PPA of digital circuits, as Figure 1.2 shows. Currently, these PPA gains are realized via time consuming and bug-prone manual RTL optimization and design space exploration.

Borrowing terminology from a former EDA tool [11], we refer to this challenge as behavioral

synthesis. More precisely, behavioral synthesis will refer to the process of transforming behavioral RTL, the sort of code written without considering PPA targets, into highly optimized RTL, for example after an expert RTL engineer has optimized the behavioral design. For the same reasons that HLS claims to improve circuit quality in design domains it is well suited to [6], automating behavioral synthesis also expands design space exploration resulting in better quality circuit designs. It also takes a large step towards realizing the productivity gains promised by HLS tools, reducing the engineering effort required to produce an optimized implementation. By its nature, behavioral synthesis takes larger steps through the design space, introducing a potentially challenging associated verification problem.

The automation of behavioral synthesis could be tackled in one of two ways: equipping HLS tools with the ability to capture and perform low-level hardware design optimizations, or by building upon existing RTL design flows. This PhD elected to deploy the latter approach. By operating on RTL, the techniques developed can be applied to both the human-written and automatically generated RTL, providing an opportunity for immediate industrial impact.

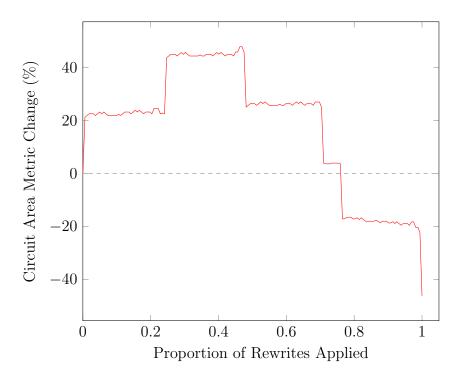

A key observation is that manual behavioral synthesis is typically performed by applying a number of known 'useful' transformations to a design. These transformations, and their domain of validity, are accumulated through years of engineer design experience. In combination, these transformations may result in substantial changes to the underlying RTL. Apart from some simple transformations implemented automatically in modern ASIC design tools [8], the process of determining a sequence of transformations to apply to an RTL design is currently based on designer intuition [12], largely due to the non-convex nature of the design space: it is often necessary to apply an early transformation that results in a worse-quality circuit before then applying a later one leading to an overall improvement. Figure 1.3 illustrates an example where it is necessary to initially apply transformations that increase circuit area cost via operator duplication or replacement, but eventually lead to subsequent area saving transformations such as arithmetic simplification or clustering, providing a net area reduction [13].

This thesis outlines an approach to automate and verify the results of behavioral synthesis for datapath circuits. Such an approach removes the need for manual RTL optimization, and

Figure 1.2: An area delay profile of the competing synthesis tools and human implementations of an Intel Media Kernel.

Figure 1.3: Progression of design cost throughout RTL rewriting for the Weight Calculation benchmark (described in Section 3.5). The plot shows the percentage change in the circuit area metric compared to the original design at every point in the rewrite chain. The area metric may converge non-monotonically.

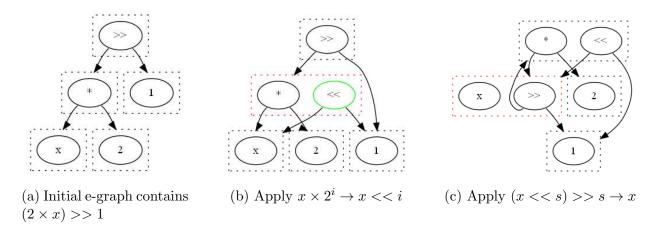

enables greater design space exploration. The robust verification flow ensures that engineers can deploy the resulting circuit designs with full confidence. At the core of the approach is a technique from the programming languages community, equality saturation [14, 15]. Equality saturation addresses the challenge of determining an optimal transformation order leveraging the e(quivalence)-graph data structure, which is capable of exploring, in parallel, all possible transformation orderings, deferring the selection of the optimal ordering until a later stage. This thesis describes the application of equality saturation to behavioral synthesis and verification, and describes several general purpose extensions to the underlying equality saturation technology.

### 1.1 Problem Statements

This thesis focuses on two primary problems, an optimization problem and a verification problem. An important definition will be that of functional equivalence. Two circuits are functionally equivalent,  $R \simeq R'$ , if and only if for all possible inputs, all outputs of R and R' are equal.

#### **Problem 1: Circuit Optimization**

Given a design in the form of an RTL implementation R, find an RTL implementation R' that minimizes cost(R') for some cost function, such that  $R \simeq R'$ .

#### **Problem 2: Circuit Verification**

Given two designs in the form of RTL implementations,  $R_1$  and  $R_2$ , mathematically prove that they are functionally equivalent,  $R_1 \simeq R_2$ , or produce an input (or sequence of inputs) for which the two circuits produce distinct results (a counter-example).

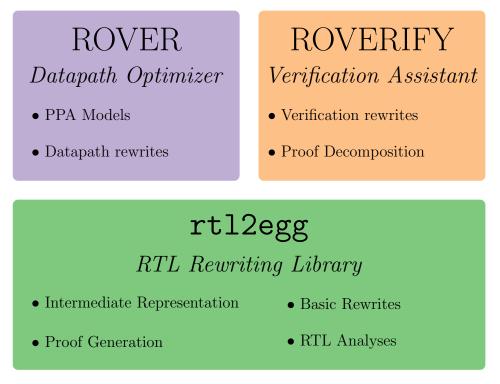

Figure 1.4: A diagrammatic representation of the library and tool suite developed.

## **1.2** Contributions

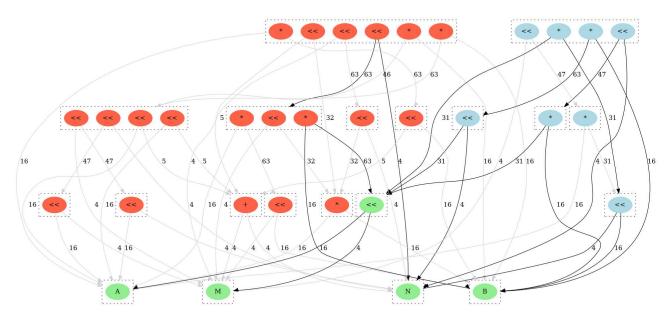

My PhD can be separated into a set of theoretical contributions and a suite of libraries and tools that apply the theory to digital circuit design and verification challenges. The theoretical developments were driven by an objective to express and evaluate hardware specific optimizations using the e-graph data structure. Firstly, an intermediate representation, VeriLang, is defined. VeriLang facilitates the representation of RTL using an e-graph and permits the description of multi-precision transformations, as described in Chapter 3. To further e-graph based analysis of digital circuits, Chapter 4 takes steps towards formalizing the connection between equality saturation and abstract interpretation, a key theory underpinning much of program analysis. To truly automate the techniques used by expert designers, a way to automatically reason about constraints present within the designs is essential. Chapter 5 introduces an approach to express sub-domain equivalences within an e-graph, enabling constraint-aware optimization.

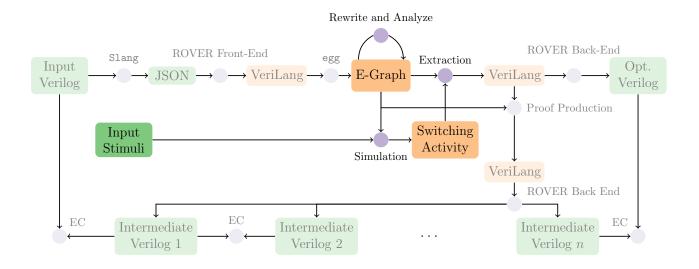

Each of the theoretical contributions has been practically realized via a suite of digital circuit design and verification tools. At the foundation of this suite, is the rtl2egg library, built on-top of the egg e-graph library [15]. The rtl2egg library provides interfaces to map (System) Verilog

to and from the egg library, via the VeriLang intermediate representation. It is also capable of generating associated proof certificates that can be checked using commercial verification tools to guarantee the correctness of its output. Beyond interfaces, rtl2egg implements a set of basic equivalence preserving RTL rewrites and RTL analyses.

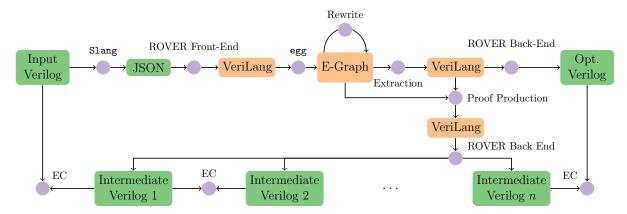

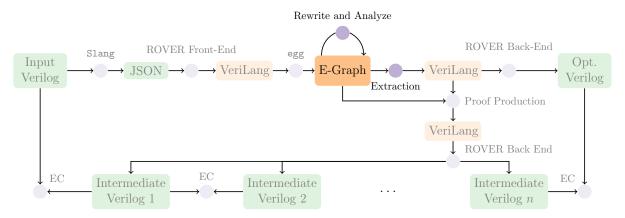

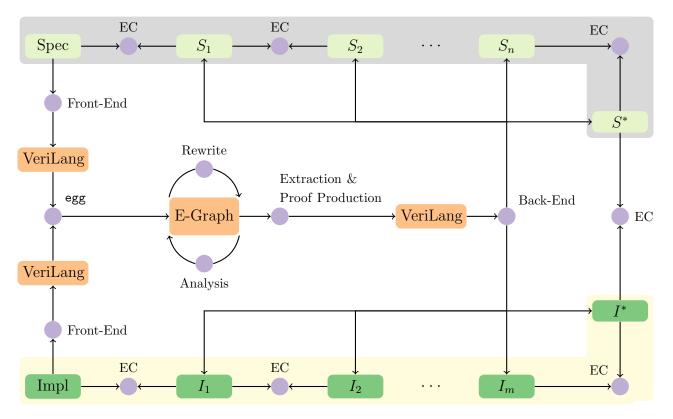

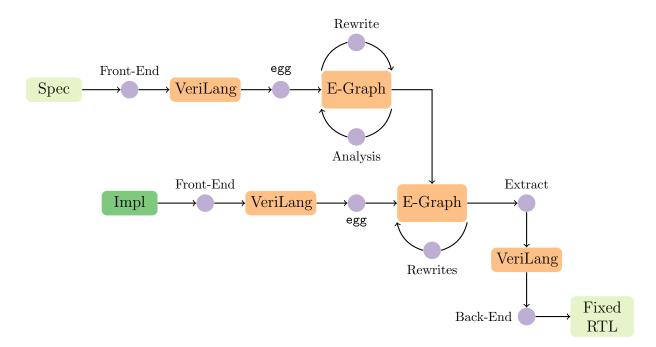

A pair of applications are implemented on-top of rtl2egg. First, ROVER, an RTL optimization engine targeting word-level datapath circuit designs, initially developed to minimize circuit area (Chapter 3). ROVER later gained circuit analysis capabilities that leverage the formal framework described in Chapter 4. Taking advantage of circuit properties discovered via the analyses, ROVER later optimized circuit performance (Chapter 5) and power (Chapter 6). The second tool, ROVERIFY (Chapter 7), a formal verification assistant, is capable of automating proof decomposition for equivalence checking of an RTL implementation against an RTL specification. The complete software suite is illustrated in Figure 1.4. The remainder of the thesis will focus on the techniques and applications themselves rather than the software implementation details.

The most substantial contributions of the thesis are summarized as follows:

- the application of equality saturation to Register Transfer Level (RTL) datapath PPA optimization,

- multi-bitwidth and multi-signage rewrites that enable datapath design space exploration capturing the connection between optimal architecture selection and bitwidth,

- an automated method to generate necessary and sufficient conditions for RTL rewrites using formal verification tools,

- a robust method to verify the correctness of the generated RTL based on automated proof decomposition,

- a formal framework to enable program analyses on an e-graph,

- an accurate value range analysis for bitvector arithmetic in RTL designs,

- a general purpose encoding of multiple equivalence relations and constraint-aware optimization via e-graph rewriting,

- a computationally-efficient methodology to simulate a large set of design choices, leveraging the compact e-graph representation,

- a word-level e-graph framework that composes a set of sub-problems from local rewrites to assist formal verification tools.

### **1.3** Implementation and Evaluation

The industrial setting in which the research was conducted means that it is not possible to opensource the software implementation. This action avoids the risk of valuable Intel Intellectual Property (IP) becoming publicly available, a risk given the use of production Intel designs as benchmarks. Despite the lack of accompanying software, this thesis discloses the techniques necessary to reproduce the results presented throughout. In fact, there have already been several reproductions of elements of this thesis for use as a baseline comparison [16] or as an optimization engine in a circuit synthesis flow [17].

The research is evaluated using a combination of open-source designs taken from prior works and Intel-provided closed-source designs. A lack of standard and industrially relevant datapath benchmarks meant that it was necessary to compile relevant benchmark suites throughout this thesis. A summary of the benchmarks used is provided in Appendix A. Each chapter motivates the benchmark selection used to evaluate that project.

### 1.4 Thesis Outline

The thesis is organized into the following chapters.

Chapter 2 introduces the necessary background on digital circuit design and verification.

From the field of programming languages, equality saturation and the theory underpinning program analysis are both described.

- **Chapter 3** provides a first introduction to ROVER, describing the foundations of an e-graph based RTL rewriting framework, which is applied to circuit area minimization.

- Chapter 4 formalizes the connection between e-graph rewriting and program analysis. To demonstrate broader applicability, the theory is used to derive tight bounds on arithmetic expressions.

- Chapter 5 introduces the theory needed to encode constraint-aware optimization within an e-graph. ROVER is extended to incorporate constraint-awareness allowing the tool to discover highly optimized floating-point arithmetic components.

- **Chapter 6** completes ROVER's understanding of the key circuit design metrics, developing a power model and associated power reduction rewrites, which are combined with the existing arithmetic optimizations.

- Chapter 7 tackles the verification problem, describing the application of the underlying RTL rewriting framework resulting in an automated verification assistant, ROVERIFY, and an automatic bug fixing tool, ROVERIFIX.

### 1.5 Publications

The research in this thesis has been the subject of the following publications:

ARITH 2022 & TCAD 2024 The first publication of the PhD was presented at the 29<sup>th</sup> ARITH and described the foundations of ROVER, presenting an initial application of equality saturation to datapath synthesis. The conference paper was nominated for a best paper award but did not win. It was later followed up with a IEEE Transactions on Computer-Aided Design of Integrated Circuits & Systems (TCAD) journal extension, which forms the basis of Chapter 3.

Automatic Datapath Optimization using E-Graphs, Samuel Coward, Theo Drane, and George A. Constantinides, IEEE 29<sup>th</sup> Symposium on Computer Arithmetic (ARITH) 2022, best paper candidate

ROVER: RTL Optimization via Verified E-Graph Rewriting, Samuel Coward, Theo Drane, and George A. Constantinides, IEEE Transactions on Computer-Aided Design of Integrated Circuits & Systems 2024

**SOAP 2023** During a brief interlude from circuit design tools, the connection between equality saturation and abstract interpretation was explored, resulting in a short paper on the subject at a program analysis workshop. The workshop paper forms the basis of Chapter 4.

Combining E-Graphs with Abstract Interpretation, Samuel Coward, George A. Constantinides and Theo Drane, Proceedings of the  $12^{th}$  ACM SIGPLAN International Workshop on the State Of the Art in Program Analysis (SOAP) 2023

DAC 2023 & TCAD 2024 Returning to circuit design tools, a new objective was set, to match manual floating-point unit design using automated tools. Such an objective led to the development of constraint-aware optimization and analysis techniques that were first published at the 60<sup>th</sup> DAC, then later followed up with a TCAD journal extension. These publications form the basis of Chapter 5.

Automating Constraint-Aware Datapath Optimization using E-Graphs, Samuel Coward, Theo Drane, and George A. Constantinides, 60<sup>th</sup> Design Automation Conference 2023 Constraint-Aware E-Graph Rewriting for Hardware Performance Optimization, Samuel Coward, Theo Drane, and George A. Constantinides, IEEE Transactions on Computer-Aided Design of Integrated Circuits & Systems 2024

FMCAD 2023 The automation of deeper datapath optimizations, highlighted limitations of the formal verification tools which were relied upon to prove the correctness of ROVER's output. To address these limitations, an automated verification assistant, ROVERIFY, was developed on-top of the rtl2egg library and was presented at FMCAD in 2023. This paper forms the basis of Chapter 7. Datapath Verification via Word-Level E-Graph Rewriting, Samuel Coward, Emiliano Morini, Bryan Tan, Theo Drane, and George A. Constantinides, in Formal Methods in Computer-Aided Design 2023

ARITH 2024 The final project of the PhD considered power optimization as a first class citizen. By combining arithmetic and power optimizations, entirely new optimal architectures were discovered, that reduce dynamic power consumption at minimal area penalty. The work was presented at the 31<sup>st</sup> ARITH and was nominated for a best paper award but did not win. This paper forms the basis of Chapter 6.

Combining Power and Arithmetic Optimization via Datapath Rewriting, Samuel Coward, Theo Drane, Emiliano Morini and George A. Constantinides, in IEEE 31<sup>st</sup> Symposium on Computer Arithmetic (ARITH) 2024, best paper candidate

## Chapter 2

## Background

This thesis leverages and extends theory from the programming languages community, applying it to problems in digital circuit design, with a specific focus on datapath circuit design and verification. Sections 2.1 and 2.2 provide the necessary background on both manual and automated approaches to these two challenges. From the field of programming languages, the thesis builds upon the e-graph data structure and explores how to apply program analysis techniques to digital circuit design problems. Section 2.3 introduces program analysis and, in particular, abstract interpretation, a key theory underpinning program analysis. Section 2.4 introduces the e-graph and equality saturation, providing a review of recent developments and applications in the area.

### 2.1 Datapath Circuit Design

Circuit design is often categorized into control flow and datapath design. Datapath circuits apply pre-defined operations on incoming data to perform some desired computation. Such circuits are often dominated by arithmetic operators, and the rate at which such arithmetic operations can be performed determines key silicon metrics, for example, floating point operations per second (FLOPS). Control flow circuits provide the orchestration, determining what operations the datapath circuits execute and where the computed results are needed. This thesis will be dedicated entirely to datapath design and verification, because such circuits implement the critical computational elements of a computer chip. However, the general purpose design techniques presented may also be applicable to control flow circuits.

Digital circuit designs may be physically implemented via programmable logic, for example on a Field Programmable Gate Array (FPGA), or via an Application Specific Integrated Circuit (ASIC), which is built to execute some fixed instruction set, for example a Graphics Processing Unit (GPU). The design of digital circuits must take into account the chosen implementation platform, since the resource constraints and performance characteristics are highly dependent upon this choice. As such, ASIC and FPGA design tools have diverged substantially. This thesis studies the design of digital circuits implemented as an ASIC.

The datapath design background is separated into four subsections. Firstly, Section 2.1.1 reviews industrial and academic contributions to automated datapath design at the RT-level. Next, Section 2.1.2 reviews manual datapath design research, as the thesis describes the automation of many of these techniques. Specializing further, Section 2.1.3 describes low-power RTL design techniques. Lastly, Section 2.1.4 surveys higher-level techniques for digital circuit design.

#### 2.1.1 RTL Synthesis

As described in the introduction, RTL is one of the most common design abstractions for digital circuit design, providing a cycle-accurate description of the circuit's behavior. RTL is written using an HDL, most commonly Verilog, System Verilog or VHDL. Such languages allow digital circuit designers to express low-level functions in terms of Boolean operators, usually called gate-level design. However, the languages also permit word-level descriptions using arithmetic operators such as addition and multiplication. For maintainability, portability and ease of verification, designers are encouraged to write at the higher word-level abstraction. For greater performance and circuit efficiency, skilled engineers may turn to gate-level implementations that provide the maximum level of expressibility. In reality, industrial HDL is typically a mixture of these abstractions. The RTL, described in HDL, is then passed to a logic synthesis tool, which synthesizes a functionally equivalent netlist [18]. The netlist describes the circuit in terms of low-level cells connected by physical wires, where each cell is comprised of potentially many transistors.

Industrial, closed-source, logic synthesis tools such as Synopsys' Design Compiler [8] and Cadence's Genus [19], currently dominate the semiconductor sector. In the open-source community, the Yosys framework is the leading RTL synthesis [9] solution, with a growing ecosystem based around the OpenRoad project [20].

Efficient datapath design can have a significant impact on PPA, providing opportunities to share or re-use resources, reduce the logic depth or avoid redundant computations. As in all compilation tasks, higher-abstractions offer downstream tools greater flexibility and potentially permit more complex optimization. In particular, for word-level RTL designs, the logic synthesis tool must determine how to map higher-level operations such as addition into a low-level logic cells [21]. Such arithmetic components have been the subject of extensive study [22], providing a huge set of component level implementations to choose from.

Of crucial importance in ASIC designs is the avoidance of carry-propagation, since this is generally an expensive operation because the circuit must be able to propagate a carry from the least-significant to the most-significant bit. Carry-propagate adders are typically required at the output of any arithmetic operation, but can be avoided by deploying carry-save format [21]. Carry-save format stores the output of an arithmetic operation in a redundant format using two signals, a carry and a save. By grouping arithmetic operations into datapath blocks, the number of expensive carry-propagate adders can be minimized, replacing them with a compressor tree. This approach will be described further in Section 2.1.2.

The initial passes in modern industrial logic synthesis tools aim to extract the largest possible datapath blocks from the design, minimizing the number of carry-propagate adders [23, 21]. A datapath block can be viewed as a sequence of arithmetic operations in a dataflow design where all intermediate results can be stored in a redundant carry-save format. The success of this stage of the compilation flow is highly dependent upon the input RTL design, since the industrial tools do not substantially modify or re-order the word-level dataflow graph. As a

result, the question of how best to formulate the RTL such that synthesis tools can maximally deploy their optimizations has received some research attention [24]. Industrial logic synthesis tools do perform some more standard optimizations such as constant folding and sub-expression sharing [21]. Since these tools are closed-source, understanding their capabilities is challenging. Automated flows that generate outputs to be consumed by these tools must make design choices based on a model of the logic synthesis tool's capabilities. This introduces a correlation problem between the internal model of logic synthesis and the logic synthesis tool itself.

A notable academic contributor in this field is Dr. Ajay Kumar Verma from EPFL. By using a set of rewriting rules, Verma and collaborators studied how arithmetic circuits can be re-ordered to maximally cluster additions together [24]. This approach goes beyond the datapath clustering described above, minimising the number of carry-propagations by explicitly transforming the dataflow graph. Many of the transformations described in this paper are incorporated into my work. Later work by Verma then proposed an approach that ran multiple passes over the circuit at differing levels of abstraction [12]. The separation of word and bit-level transformations allows the optimizer to explore beyond a limited local design space. Unfortunately, a pass based design flow introduces a phase-ordering problem forcing the use of heuristics to guide the exploration. The phase-ordering problem is discussed in more detail in Section 2.4. The work described in this thesis, provides a more general framework capable of expressing a broader range of RTL optimizations using an efficient search mechanism that does not depend on heuristics. My work also incorporates deeper optimization techniques involving context and value range analyses, achieving results beyond the capabilities of [24].

A semi-automated RTL design and verification environment has been developed by Carl Seger and collaborators [25, 26]. The Voss II framework provides a design visualization environment and proposes an interactive design space exploration approach, where the designer guides the application of a set of transformations, which are automatically checked.

In addition to this work tackling general circuit design optimization, there are many automated optimization methods targeting specific design instances. One well studied problem is the Multiple Constant Multiplication (MCM) hardware design challenge [27, 28]. The MCM problem asks, given a set of integer coefficients  $\{a_1, ..., a_n\}$ , what is the optimal architecture to compute the set  $\{a_1 \times x, ..., a_n \times x\}$ , where x is a variable. Competing solutions use a fixed number representation of the constants [28], often Canonical Signed Digit (CSD) representation [29], and or deploy an adder graph algorithm [27]. More recent work has formulated the problem as an integer linear programming (ILP) problem [30, 31, 32] or as Boolean satisfiability problem [33].

Specialized hardware generators form another class of automatic design tools, targeting specific problems. Elementary function implementations are typically constructed using hardware generators, with iterative [34] and piece-wise polynomial approximations being commonly deployed [35, 36]. The clustering of arithmetic operations, as described in Section 2.1.1, depends on hardware generators producing compressor trees for arrays of arbitrary shape [37, 38]. Making these custom hardware components flexible and usable by non-experts is a valuable target and one which this thesis take steps towards.

More recently, reinforcement learning (RL) has been successfully applied to the design of parallel prefix adders by researchers at NVIDIA [39]. By training an RL agent they were able to automatically generate highly optimized designs of prefix adders for a range of bitwidths. This technique proved successful and many instances of these generated circuits can be found in upcoming NVIDIA GPUs. Whilst successful such an approach deployed significant compute resources to optimize a widely used but highly specialized circuit, therefore may not be generalizable and scalable. A less mature, but potentially promising direction, is using Large Language Models to generate Verilog [40].

Clearly bespoke approaches will be able to solve such restricted domain optimization problems much more efficiently than a general approach. However, this raises the question of whether a more general approach can still reach the optimal solutions obtained by the bespoke method. This is a relevant question as instances of these specific problems can arise as components of more complex designs, which may be hidden or emerge during design space exploration. Chapter 3 will describe how to automate higher-level optimizations in an RTL rewriting framework that mitigates the logic synthesis correlation challenge and avoids the phase-ordering problem. Such a framework can be extended to incorporate custom solutions to specific problems.

## 2.1.2 Manual Datapath Design

Despite the large range of automated tools, industrial datapath design and optimization are often still manual tasks. Whilst this thesis will focus entirely on automated design, a short background on manual design is included, since the objective is to generalize and automate the type of optimizations performed by hand [38]. Over many years the computer arithmetic community has developed a large collection of highly optimized component-level designs. For example, arithmetic operations such as addition and multiplication are well-studied [22], yet composing these components and customizing them to the a particular use case remains a challenge. This section will provide a brief survey of key components that will be used throughout this thesis, as understanding the underlying architectures will help to guide automated design decisions.

A first important building block is the full-adder, which takes three input bits and produces two output bits representing their sum. Such low-level circuits can be composed to construct higher-level components, for example key datapath circuits to compute bitvector addition. The simplest and minimal circuit area implementation is a ripple carry adder, where full-adders are chained together to produce the sum of two bitvectors [22]. Many faster adders have been proposed [38], but of particular importance is the parallel prefix structure [41] that facilitates the decomposition into a logarithmic tree structure. Through standard bitvector manipulations, subtraction can also be implemented using these same structures. The design of addition circuits is well covered in numerous textbooks [22, 29, 38].

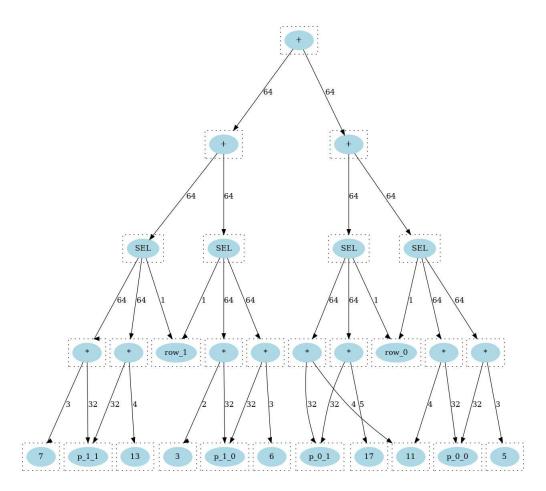

Unsurprisingly, via the schoolbook approach, multiplication can be decomposed into a sequence of additions. However to improve performance it is most commonly separated into three stages. First, an array creation stage, where each row of the array represents the product of one operand with a single (or potentially multiple) bits of the other operand. The height of this array is then reduced to just two rows using a compressor tree [42, 43], comprised of compressor cells such as the full-adder [38]. Lastly, a bitvector adder sums the remaining two rows. Once again, there has been significant research into fast and area efficient multiplication circuits, in particular looking at alternative encoding schemes to reduce the height of the multiplication array, all of which are covered in textbooks on the subject [22, 29, 38].

These fundamental arithmetic operators can be modified and extended to perform other operations. Of particular importance is the compound adder [38], which, for minimal overhead can produce both a + b and a + b + 1. At first, this may not be obviously useful. However this compound adder can be used to efficiently compute an absolute difference (deployed in Chapter 5) and an optional pre-rounding for floating-point hardware. More complex components such as a leading zero counters, detectors and anticipators are also widely used [44], becoming part of standard IP libraries [45].

Floating-point hardware design increases the complexity once again, introducing an alternative mathematical meaning to different slices of the input bitvector. In particular, floating-point addition and subtraction have received significant attention [46, 47, 48]. Beyond single floating-point operations, there has been interest in larger compound components where rounding can be deferred to avoid error accumulation [49, 50, 51, 52, 53]. Such components offer a significant design space to explore, and are typically built by floating-point design experts, who understand the complex accuracy requirements of their application. This thesis will take steps towards automating this design space exploration, producing results comparable with manual implementations.

### 2.1.3 Low-Power RTL Design

Historically, low-power ASIC design has been the concern of specialized design teams targeting mobile devices. Today, the rise of power efficient mobile chips and large scale data centers has ensured that power efficiency is a key objective for almost all ASICs. Digital circuits consume energy through the charging and discharging of capacitances inherent in CMOS logic gate design. The rate of energy consumption due to logic gate switching is known as dynamic power. They also use energy at idle due to leakage currents, known as leakage power. Dynamic power is the primary concern for RTL designers, since leakage power is more heavily influenced by lower-level design choices, such as cell selection.

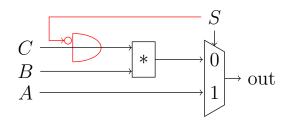

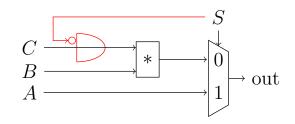

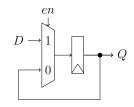

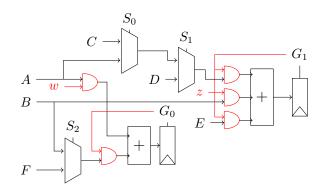

Figure 2.1: An operand isolation opportunity. The input to the multiplier can be data gated when the select signal is one, as shown by the red gate. The negated select signal,  $\sim S$  is a common input to an array of AND gates equal to the bitwidth of C.

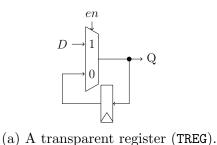

Power optimizations can be broadly separated into two groups. First, a set of optimizations that primarily target circuit area reduction, since there is a correlation between circuit area and dynamic power consumption. This is intuitive because a smaller circuit area corresponds to fewer gates and thus fewer gates to toggle. The second set of optimizations detects opportunities to switch off, or gate, sub-circuits in the design. Clock gating and operand isolation are two such optimizations. For a clock gating example, consider a pipelined floating-point adder in which exception cases, e.g. NaNs, are handled on a separate exception path. If an exceptional input is detected in the first stage, all registers on the standard input path can be gated for subsequent stages, since the result is redundant. Gating the registers stops the register outputs changing and hence prevents any toggling of the downstream combinational logic. The additional gating logic adds an area (and possible delay) overhead which must be evaluated alongside the data-dependent power saving. For an operand isolation example, consider Figure 2.1. In this circuit the multiplier is a redundant operation, so one of its inputs can be zeroed using an activation signal, limiting operator power consumption. We refer to this technique as data gating. Alternatively, both multiplier inputs could be "frozen" using transparent registers to eliminate redundant toggling [54, 55]. The transparent register is a synchronous component that has an enable signal, which, when high, allows the input to transparently flow through to the output. When low, the transparent register outputs the same signal as the previous clock cycle. Prior work has often implemented a transparent latch, which is a similar, asynchronous component, that instantly freezes a signal value when disabled [54, 55].

In academia, clock gating has been explored at a gate-level [56] and from a clock tree synthesis perspective [57]. A subset of industrial tools, such as Synopsys Power Compiler [58] and Cadence Joules [59], are incorporated into their proprietary logic synthesis engines and automatically perform clock-gating optimizations. The Synopsys synthesis tools also take operand switching frequencies into account when selecting arithmetic components, for example when deciding which multiplier operand to Booth encode [21]. Siemens PowerPro [60] is a standalone RTL to RTL tool that targets sequential clock gating. A limitation of these approaches is that they rely on analyzing the mux tree structure of the RTL design, which may miss opportunities as we shall see in Section 6.1.2. The automation of operand isolation has been explored at both the word-level [54] and at gate-level [55, 61], typically adding additional operators to a netlist in-order to reduce switching activity.

RTL power analysis tools typically rely on simulation to estimate power consumption of a given design. Tool users can either provide simulation stimuli or set input switching activities and static probabilities [58, 59]. For a given simulation period, the switching activity describes how frequently each bit of the given signal transitions from zero to one or vice versa, and the static probability specifies what proportion of the time that bit is expected to be in the one state. Commercial logic synthesis tools [8], take user provided simulation configurations and perform power optimizations guided by the simulation.

Much of the academic community appears to have lost interest in RTL power optimization, with few papers published in this area over the last decade. Chapter 6 attempts to reverse this trend, describing how to encode the power optimizations discussed above as local RTL rewrites and a framework to explore and evaluate the combination of power, arithmetic and area optimizations.

## 2.1.4 High-Level Synthesis

Whilst not the primary focus of this thesis, HLS provides an alternative design flow that aims to resolve many of the challenges discussed in this thesis. HLS aims to substantially raise the abstraction level of hardware design by allowing engineers to specify their circuits in languages like C. HLS tools automatically map a high-level software program into a custom hardware design in a low-level HDL, *e.g.* Verilog. A production HLS development flow comprises three steps. First, a high-level specification of an algorithm is *manually* rewritten following the recommended coding guidelines producing code that is amenable to optimization by the HLS tool. Second, the rewritten HLS program usually contains design constraints expressed via inline directives or pragmas to exploit hardware parallelism and resource sharing. The process of exploring these constraints is already semi-automated [62, 63, 64]. Finally, the optimized design constraints are sent with the HLS program to the HLS tool, which synthesizes a hardware design. The HLS tool automatically performs certain hardware optimizations, such as hardware scheduling and binding, which maps the start times of operations into clock cycles with efficient hardware resource sharing [65, 66, 67, 68]. The HLS tool also performs register retiming to achieve a high clock frequency [67, 68]. HLS tools are less mature than logic synthesis tools, with industrial leaders being Cadence's Stratus for ASIC design [6] and Vitis HLS for FPGA design [7]. In the open-source domain, LegUp [5] and Bambu [69] have been the subject of sustained research efforts.

The resulting RTL description can be fed into logic synthesis to produce a final netlist. Once again designers are faced with a problem. How to formulate the C-code such that the tool can best optimize it? Approaches such as graph neural networks [70] and genetic algorithms [71] have been applied to this problem. Both these works provide an alternative way to answer the tool correlation questions tackled in this thesis, albeit at a lower abstraction level.

Several works have even looked at how to deploy e-graphs in the HLS flow, with one work studying the decomposition of large multipliers [72]. Although not discussed in this thesis, with collaborators, I recently explored the application of techniques discussed in this thesis to HLS code optimization [73], integrating the e-graph into a mature software compilation stack.

## 2.2 Datapath Formal Verification

The design of digital circuits generates an equally important associated challenge, to determine the correctness of a given implementation. Formal verification is a mathematical approach to proving the correctness of a circuit for all possible input sequences, under some assumed operating conditions. For industrial scale circuits, such correctness guarantees cannot be obtained via simulation since the input space is too large to exhaustively test. Formal verification of datapath circuits is particularly challenging as they are subject to intense optimization effort, both automated and manual, in the design phase.

Classic formal property verification methods successfully used to verify state machines and communication protocols are not able to verify datapath dominated circuits. During the 1990's a number of Theorem Proving [74, 75, 76, 77, 78] and Symbolic Trajectory Evaluation (STE) [79] approaches were developed. These techniques involved comparison against mathematical specifications, often taken from industry standards, *e.g.* The IEEE Standard for Floating-Point Arithmetic [80]. Whilst capable of verifying complex designs, Theorem Proving and STE suffered from common downsides, a high barrier to entry and maintenance of complex code bases. One relevant work overcomes the barrier to entry by combining rewriting and theorem proving to automatically verify the correctness of gate-level multiplier designs in RTL [81, 82]. In this work, the authors deploy ACL2 verified [83] rewrites to transform optimized implementations into normalized implementations.

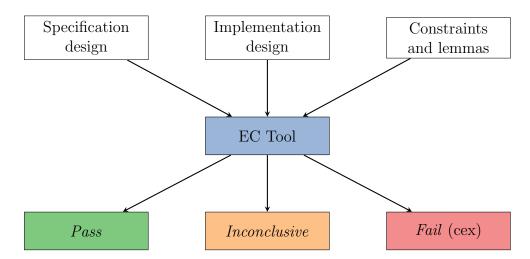

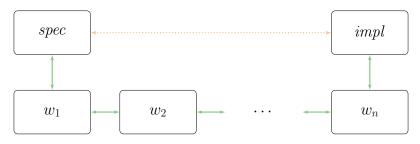

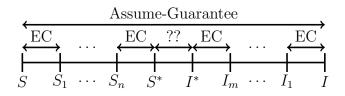

In the last decade, the circuit design industry has converged on equivalence checking (EC), defining two circuit representations to be equivalent if for all valid inputs they generate identical outputs. EC has been used in several contexts in the semiconductor industry [84, 85]. The most popular types of EC are Boolean, Sequential and Transactional. This thesis primarily focuses on Transactional EC of combinational circuit descriptions, where the result of a given computation in the *implementation* is compared against the result of the same computation in the trusted *specification*. The output of the comparison can be *Pass*, when a property is proven, *Fail*, when the property is not true (a counterexample is generated), or *Inconclusive*, when the tool does not manage to either prove or disprove a property. This setup is illustrated in Figure 2.2. Sequential EC is instead usually used to compare a version of the RTL against an altered one, for example when performance optimizations are introduced (such as clock gating) or small algorithmic changes are implemented. In this case, the cycle-accurate equivalence of the two designs is verified. Boolean EC targets gate-level verification, often comparing a synthesized netlist to an RTL implementation.

Figure 2.2: The inputs of an EC tool are two designs, a specification and an implementation, a set of constraints to drive the possible values to tests and a set of lemmas to prove. Each lemma can pass, fail or be inconclusive. A counterexample (cex) is provided for each failing lemma.